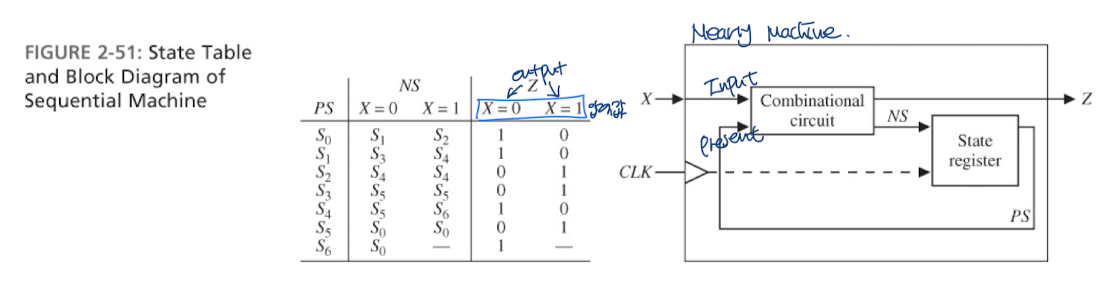

*Mealy State Machine Design `timescale 1ns/1ns module MealyStateM(Reset, Ck, X, OC, outState, Z); input Reset, Ck, X; input OC; //output buffer control output Z; wire Z; output [1:0] outState; wire [1:0] outState; localparam [1:0] S0=2'b00, S1=2'b01, S2=2'b10, S3=2'b11; reg [1:0] preState, nextState; always @ (posedge Ck) //State Register begin //sequential if (Reset) //synchronous reset preState