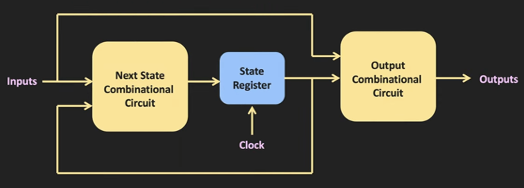

*Mealy State Machine Design

`timescale 1ns/1ns

module MealyStateM(Reset, Ck, X, OC, outState, Z);

input Reset, Ck, X;

input OC; //output buffer control

output Z;

wire Z;

output [1:0] outState;

wire [1:0] outState;

localparam [1:0] S0=2'b00, S1=2'b01, S2=2'b10, S3=2'b11;

reg [1:0] preState, nextState;

always @ (posedge Ck) //State Register

begin //sequential

if (Reset) //synchronous reset

preState <= S0;

else

preState <= nextState;

end

assign outState = (OC) ? preState : 2'bZ;

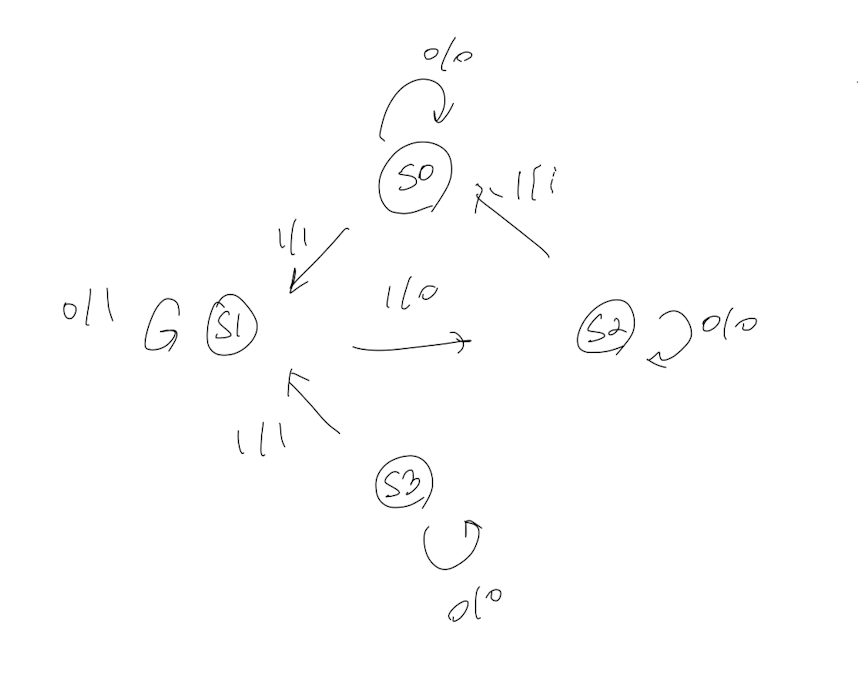

assign Z = ( ((preState == S0) && (X == 1'b1)) || //Output Combination Circuit

((preState == S1) && (X == 1'b0)) ||

((preState == S2) && (X == 1'b1)) ||

((preState == S3) && (X == 1'b1)) )

? 1'b1 : 1'b0;

always @ (*) //NextState Combination Circuit

begin // combinatinal

nextState = S0;

case (preState)

S0: if (!X) nextState = S0;

else nextState = S1;

S1: if (!X) nextState = S1;

else nextState = S2;

S2: if (!X) nextState = S2;

else nextState = S0;

S3: if (!X) nextState = S3;

else nextState = S1;

default: nextState = S0;

endcase

end

endmodule

*Mealy State Machine_Tb

`timescale 1ns/1ns

module MealyStateM_Tb;

parameter tlimit = 400;

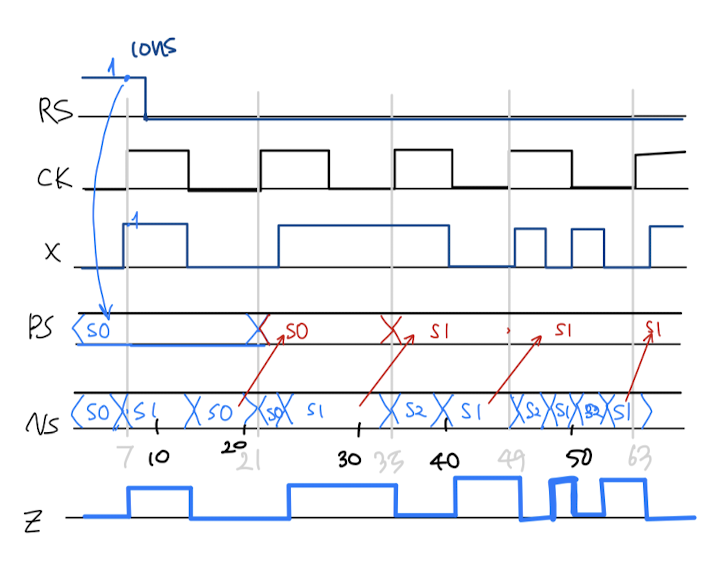

parameter ckPeriod = 7;

reg Reset = 1'b1, Ck = 1'b0, X=1'b0, OC = 1'b0;

wire [1:0] outState;

wire Z;

MealyStateM U(Reset, Ck, X, OC, outState, Z);

initial begin

#10 Reset = 1'b0; OC = 1'b1;

end

initial #tlimit $stop;

always #ckPeriod Ck = ~Ck;

always #10 X = $random;

integer result;

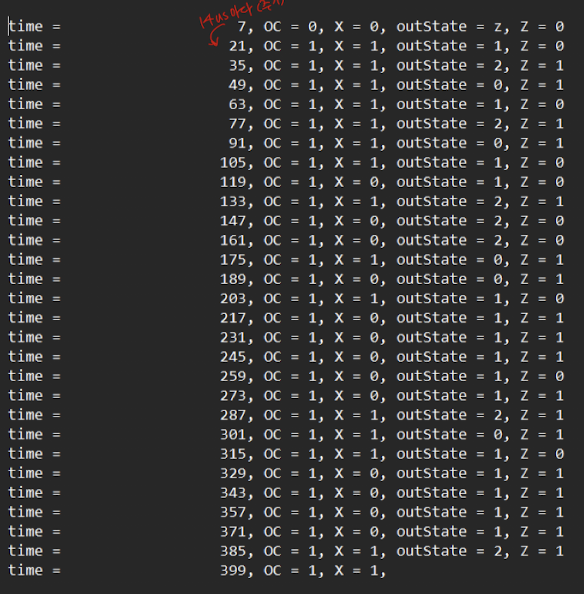

always @(posedge Ck) begin

result = $fopen ("result.txt");

$fwrite (result, "time = %d, OC = %d, X = %d, ", $time, OC, X);

#2;

$fdisplay (result, "outState = %d, Z = %d", outState, Z);

end

endmodule

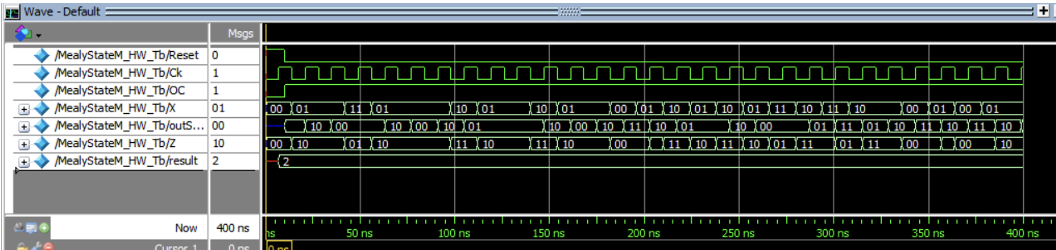

*Simulation result

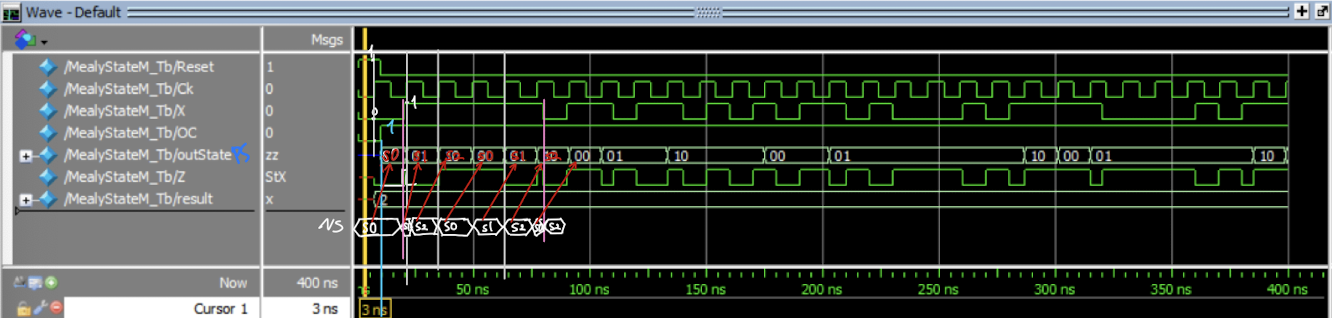

*Simulation result - Waveform

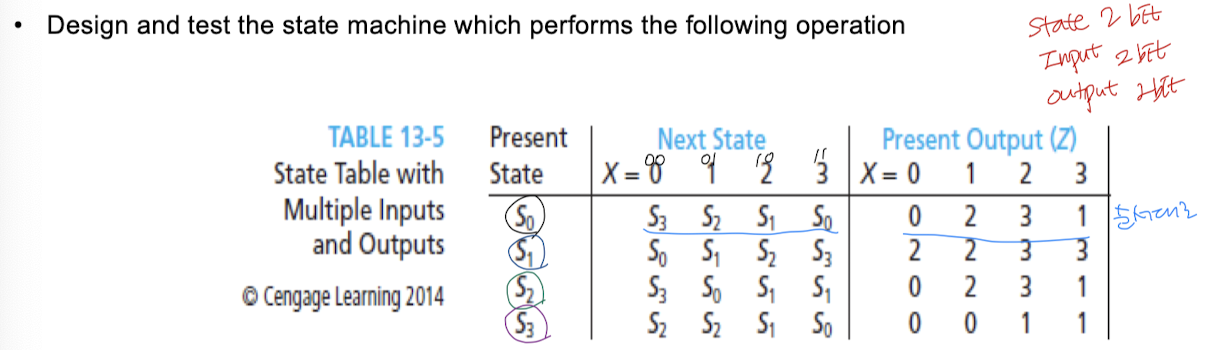

*Exercise

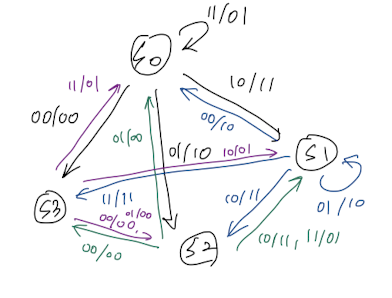

(1)Mealy State Machine Design

`timescale 1ns/1ns

module MealyStateM_EX(Reset, Ck, X, OC, outState, Z);

input Reset, Ck;

input [1:0] X;

input OC; //output buffer control

output [1:0] Z;

reg [1:0] Z;

output [1:0] outState;

wire [1:0] outState;

localparam [1:0] S0 = 2'b00, S1 = 2'b01, S2 = 2'b10, S3 = 2'b11;

reg [1:0] preState, nextState;

always @ (posedge Ck) begin //sequential

if (Reset) //Synchronous Reset

preState <= S0;

else preState <= nextState;

end

assign outState = (OC) ? preState: 2'bZ;

always @(*) begin //combinational

nextState = S0;

case (preState)

S0: case(X)

2'b00: begin nextState = S3; Z = 2'b00; end

2'b01: begin nextState = S2; Z = 2'b10; end

2'b10: begin nextState = S1; Z = 2'b11; end

2’b11: begin nextState = S0; Z = 2'b01; end

endcase

S1: case(X)

2'b00: begin nextState = S0; Z = 2'b10; end

2'b01: begin nextState = S1; Z = 2'b10; end

2'b10: begin nextState = S2; Z = 2'b11; end

2’b11: begin nextState = S3; Z = 2'b11; end

endcase

S2: case(X)

2'b00: begin nextState = S3; Z = 2'b00; end

2'b01: begin nextState = S0; Z = 2'b10; end

2'b10: begin nextState = S1; Z = 2'b11; end

2’b11: begin nextState = S1; Z = 2'b01; end

endcase

S3: case(X)

2'b00: begin nextState = S2; Z = 2'b00; end

2'b01: begin nextState = S2; Z = 2'b00; end

2'b10: begin nextState = S1; Z = 2'b01; end

2’b11: begin nextState = S0; Z = 2'b01; end

endcase

default: begin nextState = S0; Z = 2'b00; end

endcase

end

endmodule

(2) Mealy State Machine_Tb

`timescale 1ns/1ns

module MealyStateM_EX_Tb;

parameter tlimit = 400;

parameter ckPeriod = 7;

reg Reset = 1'b1, Ck = 1'b0, OC = 1'b0;

reg [1:0] X = 2'b00;

wire [1:0] outState;

wire [1:0] Z;

MealyStateM_EX U(Reset, Ck, X, OC, outState, Z);

initial begin

#10 Reset = 1'b0; OC = 1'b1;

end

initial #tlimit $stop;

always #ckPeriod Ck = ~Ck;

always @(negedge Ck) begin

X = $random;

end

integer result;

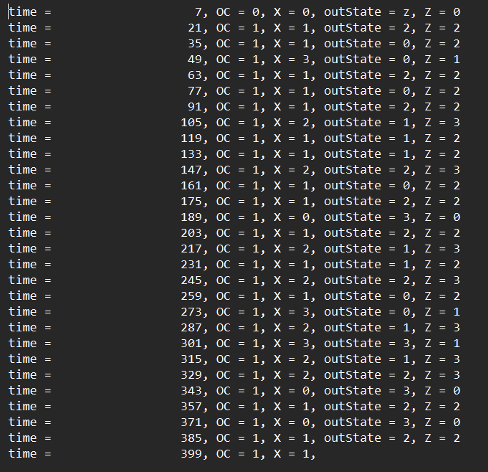

always @(posedge Ck) begin

result = $fopen ("result2.txt");

$fwrite (result, "time = %d, OC = %d, X = %d, ", $time, OC, X);

#2;

$fdisplay (result, "outState = %d, Z = %d", outState, Z);

end

endmodule

(3) Simulation result

(4) Simulation result - Waveform

'Study > Digital System Design and Lab[Verilog]' 카테고리의 다른 글

| #6 Modeling Sequential Circuits(Moore, Mealy machine) (0) | 2023.10.16 |

|---|---|

| #5 Finite State Machine - Moore, Mealy Machine (0) | 2023.10.15 |

| #5-1 Sequential Circuit Design - Finite State Machine (Moore-circuit) (0) | 2023.10.15 |

| #4-1 "IF", "Case" Statement - Counter (1) | 2023.10.15 |

| #3-2 Shift Register (0) | 2023.10.15 |