*Finite State Machine

- Finite State Machine (FSM) is abstract model of describing sequential circuit.

*Finite State Machine - Moore, Mealy Machine

*MooreState Design

Moore Machine

Moore Machine

`timescale 1ns/1ns

module MooreStateM(Reset, Ck, X, OC, outState, Z);

input Reset, Ck, X;

input OC;

output Z;

reg Z;

output [1:0] outState;

wire [1:0] outState;

lacalparam [1:0]S0 = 2'b00, S1 = 2'b01, S2 = 2'b10, S3 = 2'b11;

reg[1:0] preState, nextState;

always@(posedge Ck)

begin

if(Reset)

preState <= S0;

else

preState <= nextState;

end

assign outState = (OC) ? preState : 2'bZ;

always@(*)

begin

nextState = S0;

Z = 1'b0;

case(preState)

S0 : begin

if(X) nextState = S1;

else nextState = S3;

Z = 1'b0;

end

S1 : begin

if(X) nextState = S2;

else nextState = S0;

Z = 1'b1;

end

S2 : begin

if(X) nextState = S2;

else nextState = S1;

Z = 1'b0;

end

S3 : begin

if(X) nextState = S1;

else nextState = S2;

Z = 1'b1;

end

default : begin

nextState = S0;

Z = 1'b0;

end

endcase

end

endmodule

*MooreStateM_Tb

`timescale 1ns/1ns

module MooreStateM_Tb;

parameter tlimit = 400;

parameter ckPeriod = 7;

reg Reset = 1'b1, Ck = 1'b0, X = 1'b0, OC = 1'b0;

wire [1:0]outState;

wire Z;

MooreStateM U(Reset, Ck, X, OC, outState, Z);

initial

begin

#10 Reset = 1'b0; OC = 1'b1;

end

initial #tlimit $stop;

always #ckPeriod Ck = ~Ck;

always@(negedge Ck)

begin

X = $random;

end

integer result;

always@(outState or Z)

begin

result = $fopen("result.txt");

$fwrite(result, "time = %d, OC = %d, X = %d, ", $time, OC, X);

#2

$fdisplay(result, "outState = %d, Z = %d", outState, Z);

end

endmodule

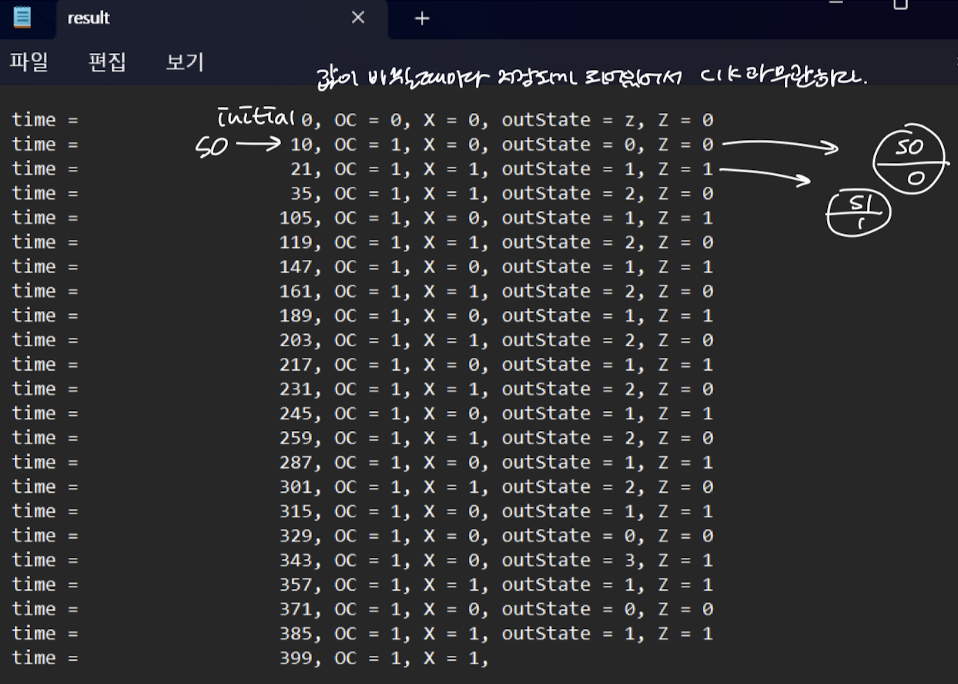

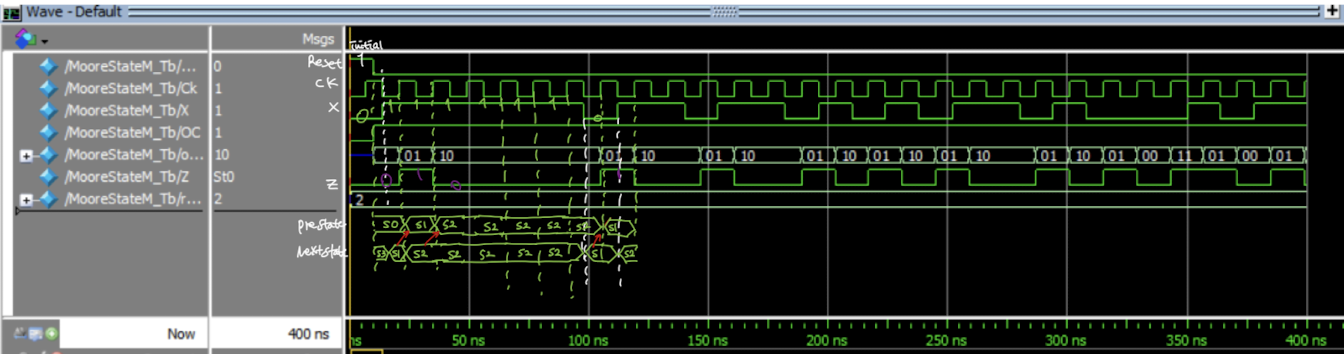

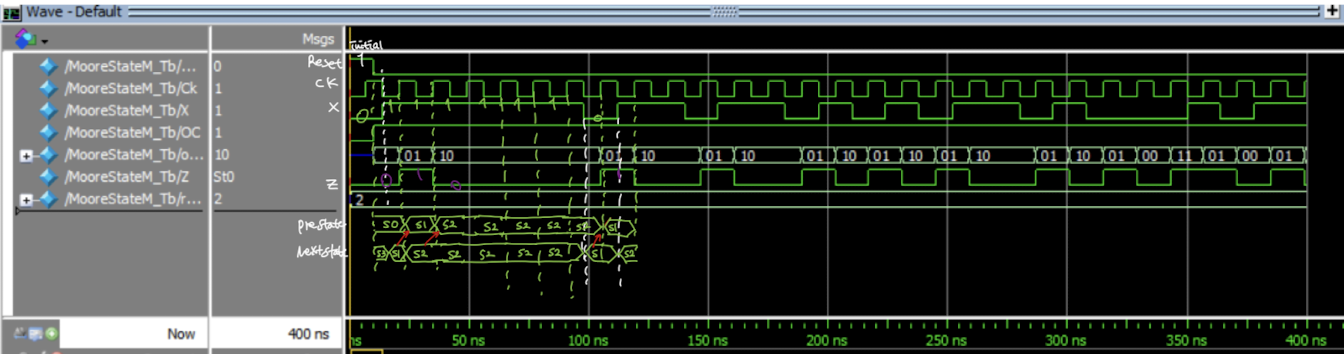

*Simulation result

| Pre State |

Next State |

Z |

| X = 0 |

X = 1 |

| S0(00) |

S3 |

S1 |

0 |

| S1(01) |

S0 |

S2 |

1 |

| S2(10) |

S1 |

S2 |

0 |

| S3(11) |

S2 |

S1 |

1 |

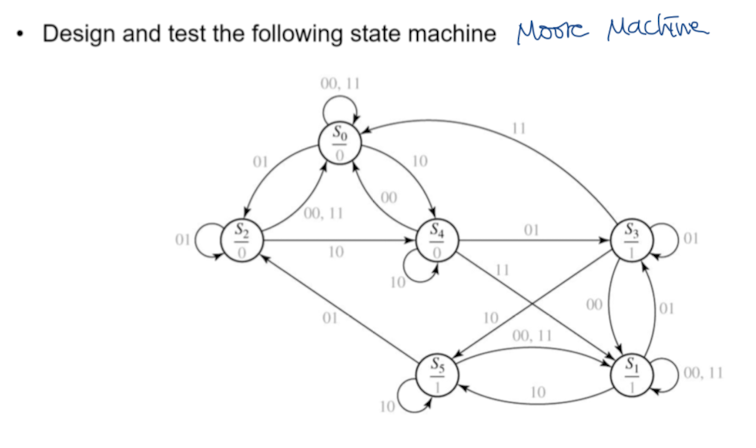

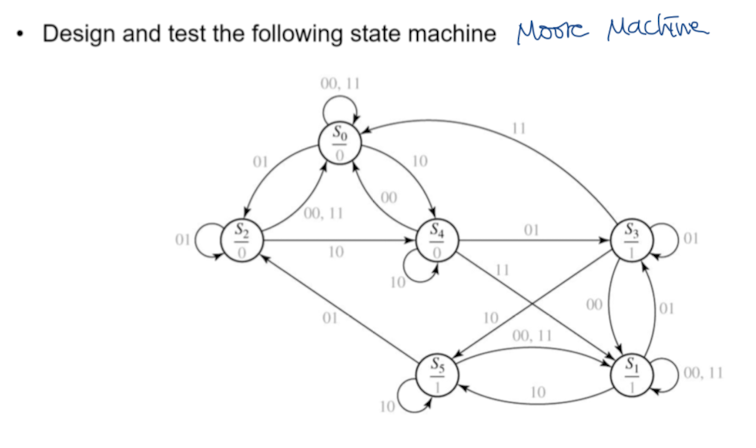

*Exercise

State : 3bit

input : 2bit

(1) MooreState Design

| PS |

NS |

Z |

| |

X = 00 |

X = 01 |

X = 10 |

X = 11 |

|

| S0 |

S0 |

S2 |

S4 |

S0 |

0 |

| S1 |

S1 |

S3 |

S5 |

S1 |

1 |

| S2 |

S0 |

S2 |

S4 |

S0 |

0 |

| S3 |

S1 |

S3 |

S5 |

S0 |

1 |

| S4 |

S0 |

S3 |

S4 |

S1 |

0 |

| S5 |

S1 |

S2 |

S5 |

S1 |

1 |

`timescale 1ns/1ns

module MooreStateMwork (Reset, Ck, X, OC, outState, Z);

input Reset, Ck;

input[1:0] X;

input OC;

output Z;

reg Z;

output[2:0] outState;

wire[2:0]outSate;

localparam [2:0]S0 = 3'b000, S1 = 3'b001, S2 = 3'b010, S3 = 3'b011, S4 = 3'b101, S5 = 3'b110;

reg[2:0] preState, nextState;

always@(posedge Ck)

begin

if(Reset)

preState <= S0;

else

preState <= nextState;

end

assign outState = (OC) ? preState : 3'bZ;

always@(*)

begin

nextState = S0;

Z = 1'b0;

case (preState)

S0: begin

if(X==2'b00)nextState = S0;

else if(X==2'b01)nextState = S2;

else if(X==2'b10)nextState = S4;

else nextState = S0;

Z = 1'b0;

end

S1: begin

if(X==2'b00)nextState = S1;

else if(X==2'b01)nextState = S3;

else if(X==2'b10)nextState = S5;

else nextState = S1;

Z = 1'b1;

end

S2: begin

if(X==2'b00)nextState = S0;

else if(X==2'b01)nextState = S2;

else if(X==2'b10)nextState = S4;

else nextState = S0;

Z = 1'b0;

end

S3: begin

if(X==2'b00)nextState = S1;

else if(X==2'b01)nextState = S3;

else if(X==2'b10)nextState = S5;

else nextState = S0;

Z = 1'b1;

end

S4: begin

if(X==2'b00)nextState = S0;

else if(X==2'b01)nextState = S3;

else if(X==2'b10)nextState = S4;

else nextState = S1;

Z = 1'b0;

end

S5: begin

if(X==2'b00)nextState = S1;

else if(X==2'b01)nextState = S2;

else if(X==2'b10)nextState = S5;

else nextState = S1;

Z = 1'b1;

end

default: begin

nextState = S0;

Z = 1'b0;

end

endcase

end

endmodule

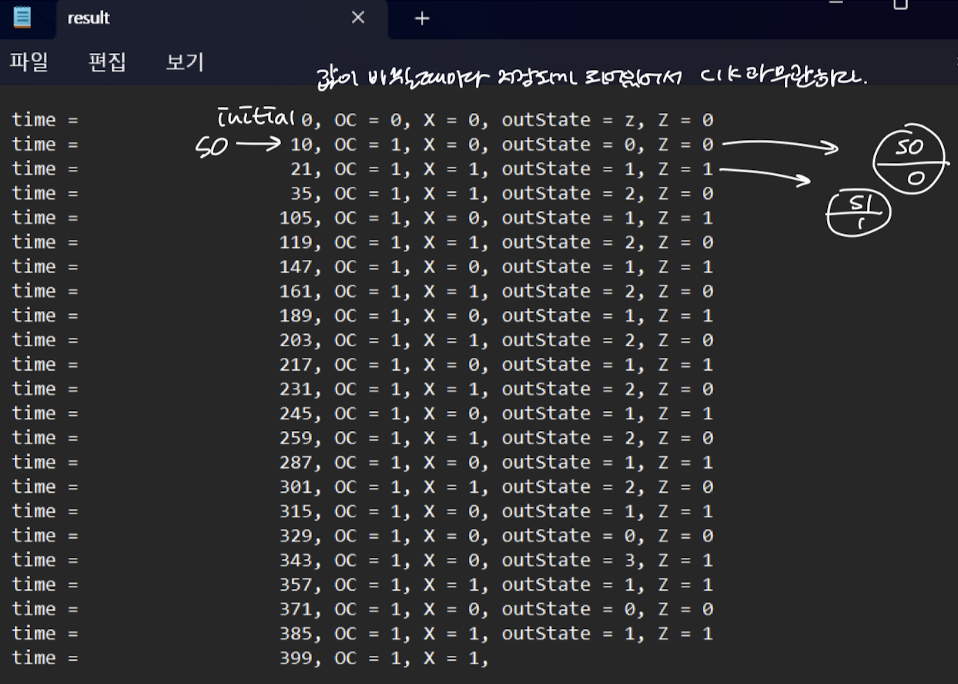

(2) MooreState Design - TB

`timescale 1ns/1ns

module MooreStateMwork_Tb;

parameter tlimit = 400;

parameter ckPeriod = 7;

reg Reset = 1'b1, Ck = 1'b0, OC = 1'b0;

reg [1:0] X = 2'b00;

wire [2:0] outState;

wire Z;

MooreStateMwork U(Reset, Ck, X, OC, outState, Z);

initial begin

#10 Reset = 1'b0; OC = 1'b1;

end

initial #tlimit $stop;

always #ckPeriod Ck = ~Ck;

always @(negedge Ck) begin

X = $random;

end

integer result;

always@(outState or Z) begin

result = $fopen("result_work.txt");

$fwrite (result, "time = %d, OC = %d, X = %d, ",$time, OC, X);

#2;

$fdisplay (result, "outState = %d, Z = %d", outState, Z);

end

endmodule