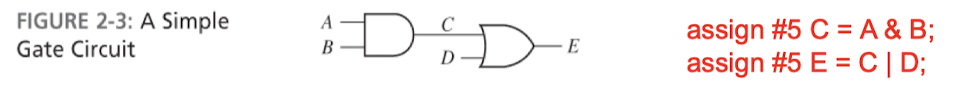

*Verilog Description of Combinational Circuits A signal assignment statement has the form : Assign [#delay] signal_name = expression; (square brackets indicate that #delay is optional) Concurrent statements (continuous assignments) examples 1-2 assign의 순서가 바뀌어도 다른 Hardware이 설계되진 않는다. (순서중요X) assign #10 A = ~A //A를 10ns 이후 inversion시켜라 => state를 바꾸는 주기적 신호 Q. A대신 CLK은 왜 사용 못하는가? A. CLK의 data type..