*Verilog Description of Combinational Circuits

- A signal assignment statement has the form

: Assign [#delay] signal_name = expression;

(square brackets indicate that #delay is optional) - Concurrent statements (continuous assignments) examples 1-2

assign의 순서가 바뀌어도 다른 Hardware이 설계되진 않는다. (순서중요X)

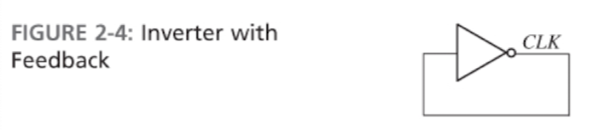

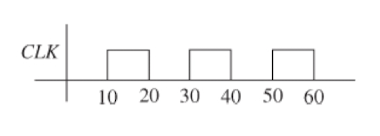

assign #10 A = ~A

//A를 10ns 이후 inversion시켜라=> state를 바꾸는 주기적 신호

Q. A대신 CLK은 왜 사용 못하는가?

A. CLK의 data type(wire or reg)두가지 인데 wire은 값을 기억하지 않고 초기값 지정 불가하다.

하지만 CLK은 초기값을 설정해줘야해서 wire사용 불가능하다.

assign [x] -> always [O]

ex) reg CLK = 0;

- Concurrent statements (continuous assignments) examples 1-2

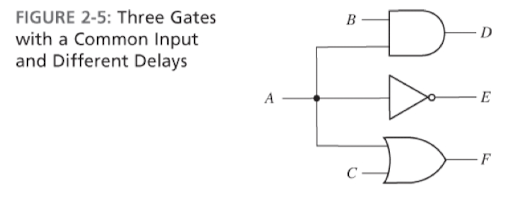

// When A changes, these concurrent statements all execute at the same time

assign #2 D = A && B;

assign #1 E = ~A;

assign #3 F = A || C;- & : 비트연산자(bitwise)

&& : 논리연산자

=> 두개의 bit차이가 달라서 &하나짜리 사용이 더 낫다.

1. 비트연산자

| : "0001 | 0000 == 0001”이 성립합니다. 즉, 하나의 비트 비교시 하나라도 1이라면 1이 됩니다.

& : |와는 다르게 두 비트 모두가 1인 경우만 1이 됩니다.즉, "0101 & 0100 == 0100”이 됩니다.

2. 논리연산자

||(or) : 하나라도 true인 경우 true를 반환합니다. 즉, “true || false == true”가 됩니다.

&&(and) : 모두 true인 경우만 true를 반환합니다. 즉, “true && true == true, true && false == false”가 됩니다.

// the hard way

assign C[3] = A[3] && B[3];

assign C[2] = A[2] && B[2];

assign C[1] = A[1] && B[1];

assign C[0] = A[0] && B[0];// the easy way assuming C, A and B are 4-bit vectors

wire[3:0] C //초기 bit할당 필요

assign C = A & B;

- Data Types

: Reg(register) and wire

Registers are used to store values.

=> continuous assignment 사용해 결과 저장되는 것을 주로 사용

Wires cannot hold a value; they are used to link modules of combinational logic. - Verilog supports data structures called arrays, memory arrays, and vectors.

: An array is a collection of objects with the same attributes (more on arrays and memory arrays later...).

: A vector is a one-dimensional array of bit signals.

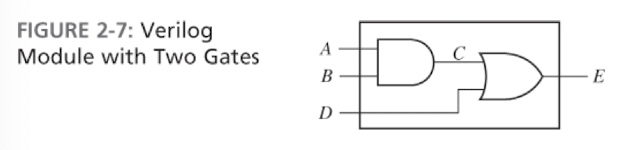

*Verilog Modules

- Module : basic building block

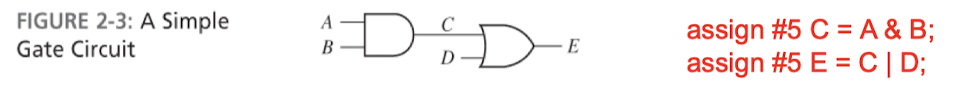

module two_gates (A, B, D, E);

output E;

input A, B, D; //input과 output 한줄로 선언 가능

wire C, E;

assign C = A && B; //concurrent

assign E = C || D; //statements

endmodule- module - endmodule : module의 시작과 끝.

- two_gates : module name.

- (A, B, D, E) : optional port list.

- output, input : the list-of-interfaceports

- Positional asociation : listing the ports in order.

=> module만들 때 선언한 변수 순서를 잘 기억해서 사용해야한다. - Named association (described in Chapter 8) : signals can be in any order as long as the signals in the module are connected to the ports by name.

- Example for a Full Adder:

2023.10.04 - [Study/Digital System Design and Lab] - #1-1 Design a full adder

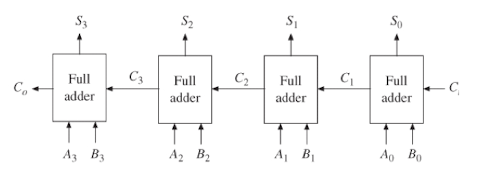

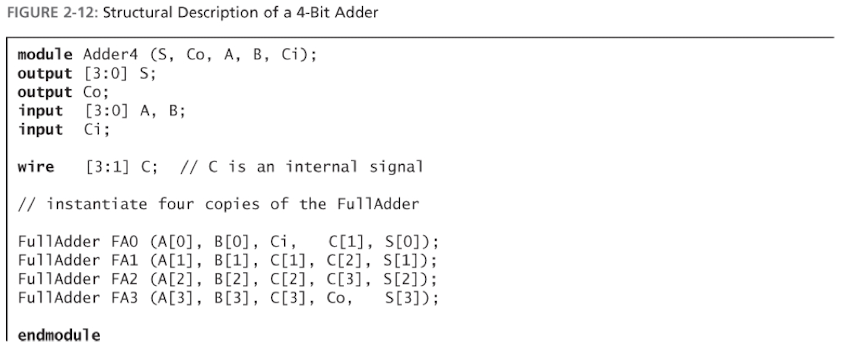

- 4-bit Adder

=> Full adder 4개를 복사해서 4 bit adder를 설계할 것이다.

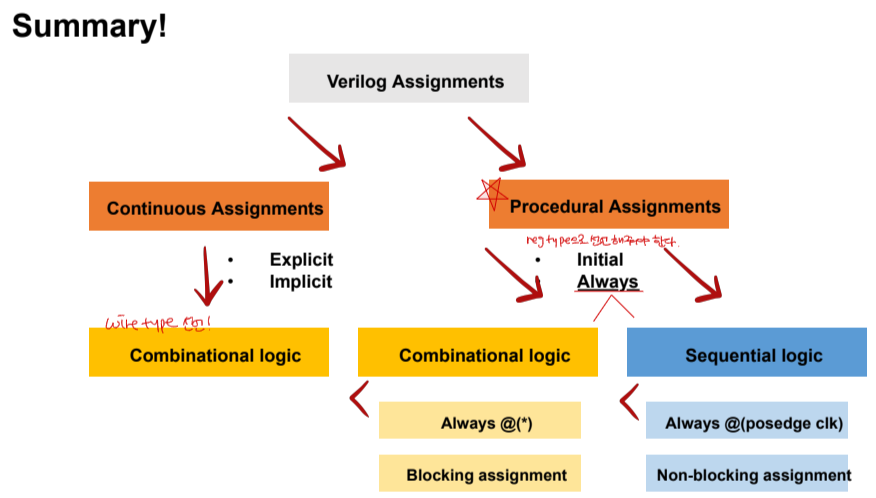

*Verilog Assignments[새로운 값 할당 방법]

- Continuous assignments : used to assign values for combinational logic circuits.

- Two types

: Explicit continuous assignments : uses the assign keyword after the net is separately declared.

=> wire A;

assign #5 A = B & C;

: Implicit continuous assignments : assign the value in declaration without using the assign keyword.

=> wire A = B & C; //assign 생략가능 - Procedural assignments : used to model registers and finite state machines using the always keyword.

=> sequential logic 설계시 주로 사용한다.(combination logic에서도 사용하기도 함)

- Two types

: Initial blocks execute only once at time zero.

=> module설계시 initial block은 잘 사용하지 않는다.

주로 test bench안에서 사용한다.

initial block은 회로로 합성이 되지 않기 때문이다.

: Always block loop to execute over and over again.

=> 조건 나올때까지 반복한다.

*Verilog Procedural Assignments

- An initial statement has the form:

initial

begin

sequentual-statements

end- An always statement has the form:

always@(sensitivity-list)

begin

sequential-statements

end- sensitivity-list : 바뀌면 always문을 수행할 것인지 오른쪽 할당된 값을 모두 써줘야 한다.

EX)

A = B + C; //A는 B와 C가 바뀌면 계산이 된다.

always@(B or C) //B와 C가 바뀔 때 아래 문장들을 수행하라

...

...

always@(*) //오른쪽 모두를 해당하는 말이 된다.

EX)

always@(posedge clk)

//가로안을 보고 combination or sequential logic인지 알 수 있다.

- begin-end : executed sequentially rather than concurrently

- Sensitivity list:

- Combinatorial always blocks:

condition statement(if문과 유사한 것)속 모든 신호들을 포함하고 오른쪽의 assignment의 모든 신호들을 포함한다.

- Sequential always blocks:

list는 3종류의 edge-triggered를 포함한다 : clock, reset, and signal event

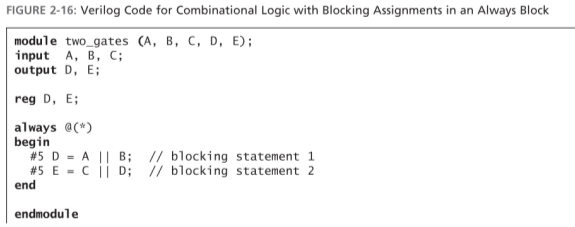

- reg D, E; : 수행되어 결과를 저장하는 부분은 reg type(저장할 수 있는 type)

- always@(*) = always@(A or B or C or D)

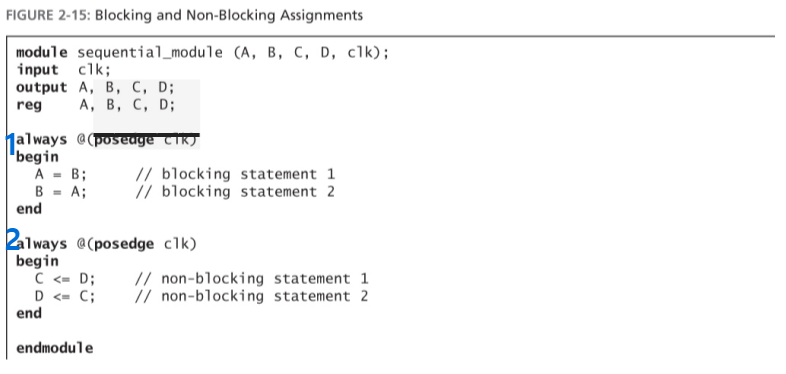

- Sequential statements can be evaluated in two different ways:

- Blocking assignment<Combinational logic에서 사용>

: sequential block에서 수행하면서 next statement로 가기 전에 오른쪽 statement를 순차적으로 수행되게 만들고 싶을 때 사용한다.

Uses the "=" operator

- Non-blocking assignment<Sequential logic에서 사용>

: always block안의 모든 문장을 한꺼번에 동시에 수행하고 싶을 때 사용한다.

Uses the "<=" operator

- 첫 번째 always는 순차적으로 수행되기 때문에

A = 3, B = 5일 때 A = 5 다음에 B = 5로 수행된다. - 두 번째 always는 동시에 수행되기 때문에

C = 3, D = 5일 때 C = 5 D = 3으로 SWIPs하게 수행된다.

- Data Types:

- Wire

: 정보를 저장할 수 없다.

: 초기 값이 다르다.

: Combinational logic일 때 사용한다.

: assign문의 좌변에 사용할 수 있지만, always@ 블록에서'=' '<=' 의 좌변에 사용할 수 없다.

- Reg

: Register은 값을 저장할 수 있다.

: 초기 값은 x(unknown)이다.

: Combinational and Sequential logic에서 사용한다.

: assign문의 좌변에 사용할 수 없지 만, always@블록에서 '=' <='의 좌변에 사용할 수 있다.

*some Verilog syntax(rules)

'Study > Digital System Design and Lab[Verilog]' 카테고리의 다른 글

| #3 Modeling Flip-Flops Using Always Block (0) | 2023.10.14 |

|---|---|

| #2-2 Multiplexer Design (0) | 2023.10.11 |

| #2-1 Design a 4-Bit Adder (0) | 2023.10.11 |

| #1-1 Design a full adder (1) | 2023.10.04 |

| #1 Digital Circuit Design (0) | 2023.10.03 |