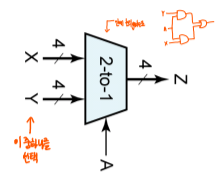

*Multiplexer Design - Conditional Expression

A conditional(if 구문) signal assignment statement has the form :

assign signal_name = condition ? expression_T : expression_F;

if else

=> 한줄로 mux를 design할 수 있다.

`timescale 1ns/1ns

module Mux(X, Y, A, Z);

input[3:0] X, Y;

intput A;

output[3:0]Z;

assign Z = (A) ? Y : X; //A=1(true)이면 Y를 추출, A = 0(false)이면 X를 추출한다

endmodule

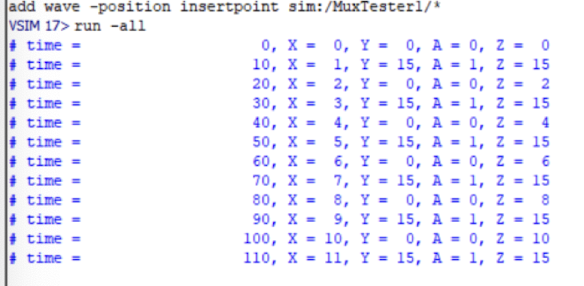

*2-to-1 Multiplexer Design(TestBench)

`timescale 1ns/1ns

module MuxTester1;

parameter tlimit = 100;

reg[3:0] X = 4'b0;

reg[3:0] Y = 4'b0;

reg A = 0;

wire [3:0]Z;

Mux U(X ,Y, A, Z);

always@(*) begin

if($time >= tlimit) $stop;

else begin

repeat(12) begin

$display("time = %d, X = %d, Y = %d, A = %d, Z = %d", $time, X, Y, A, Z);

A = ~A; //010101...이 반복 될 것

X = X + 1; //1씩 증가

Y = 15-Y; //1111과 0000이 반복해서 나올 것

#10;

end

end

end

endmodule

*2-to-1 Multiplexer Design Result

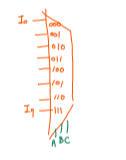

*4-to-1 Multiplexer Design(Conditional Expression)

Control input이 A, B 두개이므로 2bit사용하고 Data input이 4bit이다.

`timescale 1ns/1ns

module Mux4to1 (I0, I1, I2, I3, A, B, Z1);

input[3:0]I0, I1, I2, I3;

inputA, B;

output[3:0]Z1;

assign Z1 = ({A, B} == 2'b00 ? I0 : ({A, B} = 2'b01) ? I1 : ({A, B} = 2'b10) ? I2 : I3; //다른 두 비트 표현 {}

endmodule

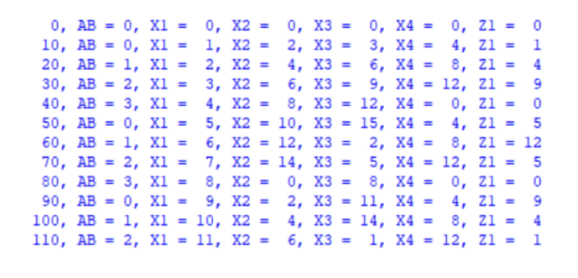

*4-to-1 Multiplexer Design(TestBench)

`timescale 1ns/1ns

module Mux4to1Tester1;

parameter tlimit = 100;

reg[3:0]X1, X2, X3, X4;

reg A, B;

wire[3:0]Z1;

Mux4to1 U1(X1, X2, X3, X4, A, B, Z1);

integer i;

initial begin

X1 = 4'b0; X2 = 4,b0; X3 = 4'b0; X4 = 4,b0, A = 1'b0; B = 1'b0;

end

always@(*) begin

if($time >= tlimit)$stop;

else begin

for(i=0; i<12; i=i+1) begin

$display ("time = %d, AB = %d, X1 = %d, X2 = %d, X3 = %d, X4 = %d, Z = %d",

$time, {A,B}, X1, X2, X3, X4, Z1);

{A,B} = i%4;

X1 = X1+1; X2 = X2+2, X3 = X3+3, X4 = X4+4;

#10;

end

end

end

endmodule*4-to-1 Multiplexer Design Result

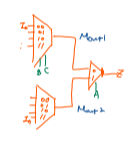

*8-to-1 Multiplexer Design(Conditional Expression)

`timescale 1ns/1ns

module Mux8to1 (I0, I1, I2, I3, I4, I5, I6, I7, A, B, C, Z);

input[3:0] I0, I1, I2, I3, I4, I5, I6, I7;

input A, B, C;

output[3:0] Z;

wire[3:0] Mout1, Mout2;

Mux4to1 U1(I0, I1, I2, I3, B, C, Mout1);

Mux4to1 U2(I4, I5, I6, I7, B, C, Mout2);

Mux U3(Mout1, Mout2, A, Z);

endmodule

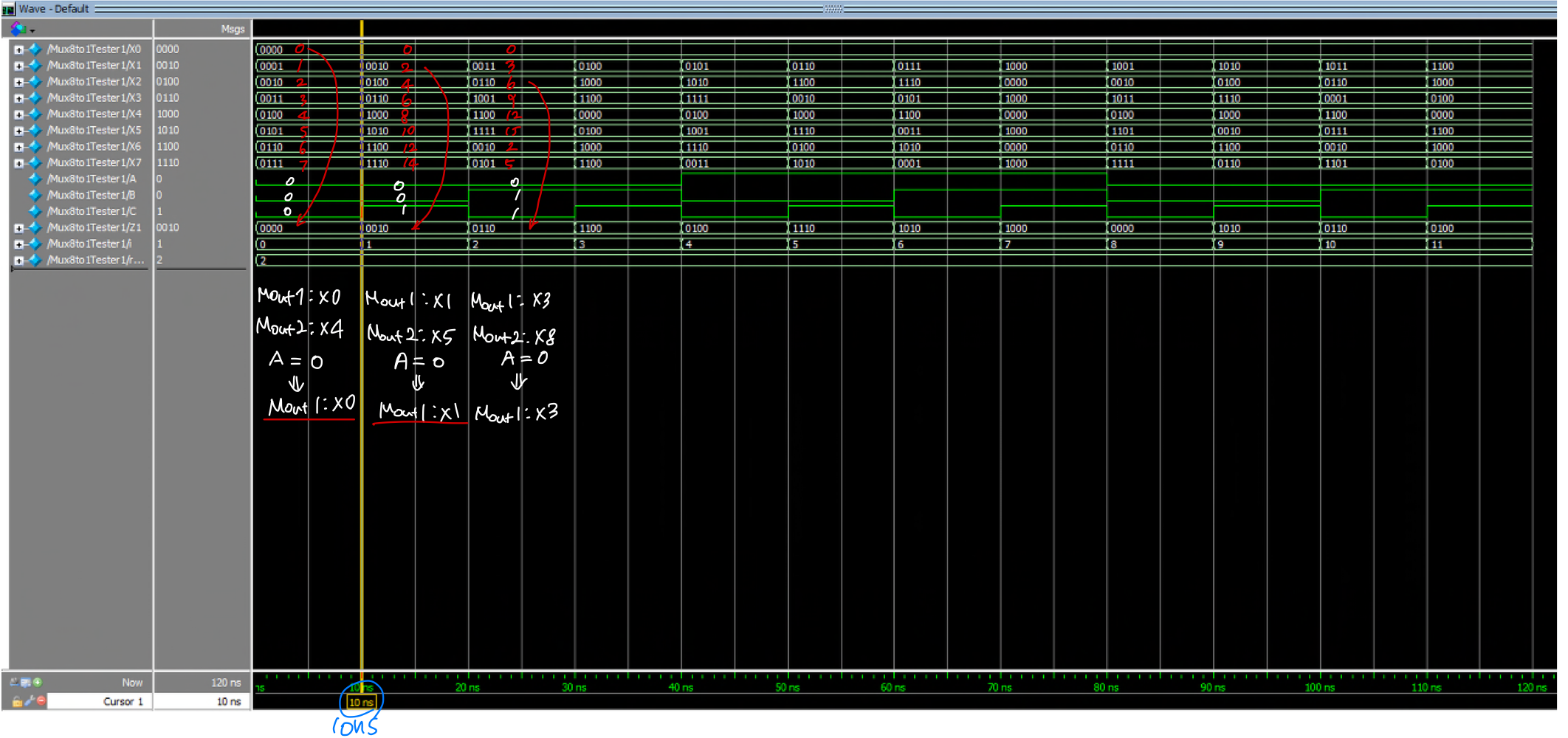

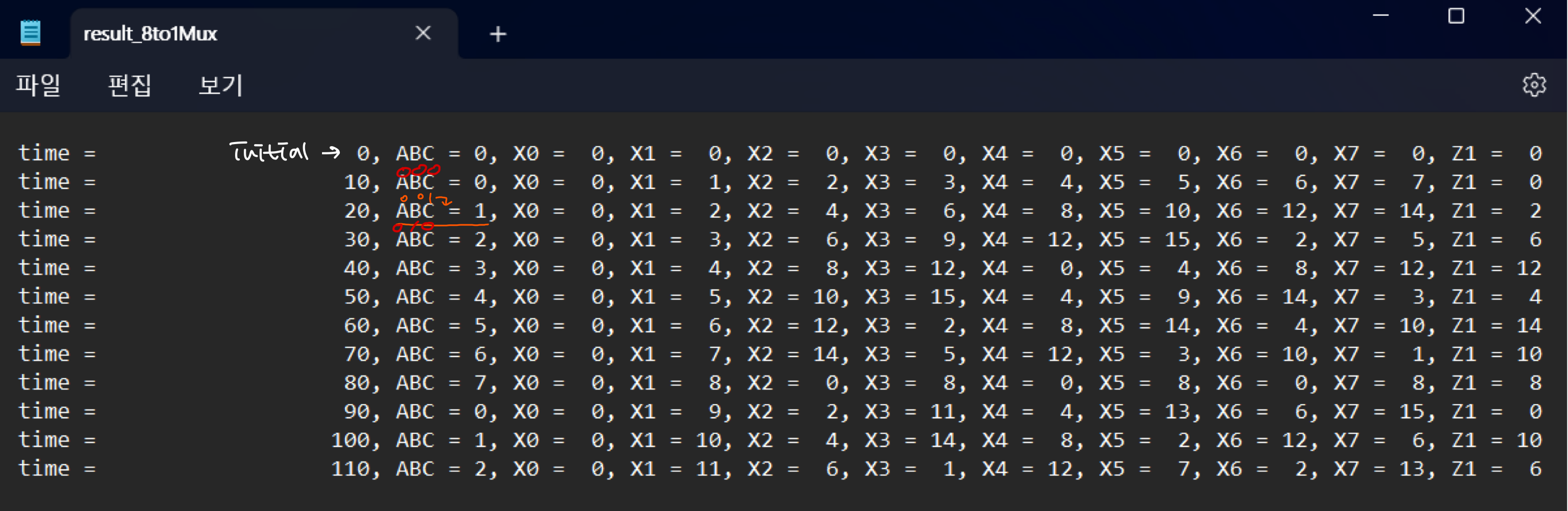

*8-to-1 Multiplexer Design(TestBench)

`timescale 1ns/1ns

module Mux8to1Tester1;

parameter tlimit = 100;

reg[3:0] X0, X1, X2, X3, X4, X5, X6, X7; //input

reg A, B, C; //Mux

wire[3:0]Z1; //output

Mux8to1 U1(X0, X1, X2, X3, X4, X5, X6, X7, A, B, C, Z1);

integer i, result; //result?

initial begin

X0=4'b0; X1=4'b0; X2=4'b0; X3=4'b0; X4=4'b0; X5=4'b0; X6=4'b0; X7=4'b0; A=1'b0; B=1'b0; C=1'b0;

end

always@(*)begin

if($time >= tlimit)$stop;

else begin

result = $fopen("result_8to1Mux.txt");

for(i=0;i<12;i=i+1) begin

$fdisplay(result, "time=%d, ABC=%d, X0=%d, X1=%d, X2=%d, X3=%d, X4=%d, X5=%d, X6=%d, X7=%d, Z1=%d",

$time, {A,B,C}, X0,X1,X2,X3,X4,X5,X6,X7,Z1);

{A, B, C} = i%8;

X0=X0+0; X1=X1+1; X2=X2+2; X3=X3+3; X4=X4+4; X5=X5+5; X6=X6+6; X7=X7+7;

#10;

end

end

end

endmodule

*8-to-1 Multiplexer Design Result

'Study > Digital System Design and Lab[Verilog]' 카테고리의 다른 글

| #4 Simple Synthesis Examples (0) | 2023.10.15 |

|---|---|

| #3 Modeling Flip-Flops Using Always Block (0) | 2023.10.14 |

| #2-1 Design a 4-Bit Adder (0) | 2023.10.11 |

| #2 Verilog Description of Digital Systems(Verilog Assignments) (0) | 2023.10.11 |

| #1-1 Design a full adder (1) | 2023.10.04 |