1. 정의

트랜지스터는 크게 접합형 트랜지스터(BJT, 전류제어, pnp와 npn으로 알려짐)와 전계효과트랜지스터(FET, Field-effect transistor, 장효과/필드효과 트랜지스터, 전압제어)로 분류할 수 있다.

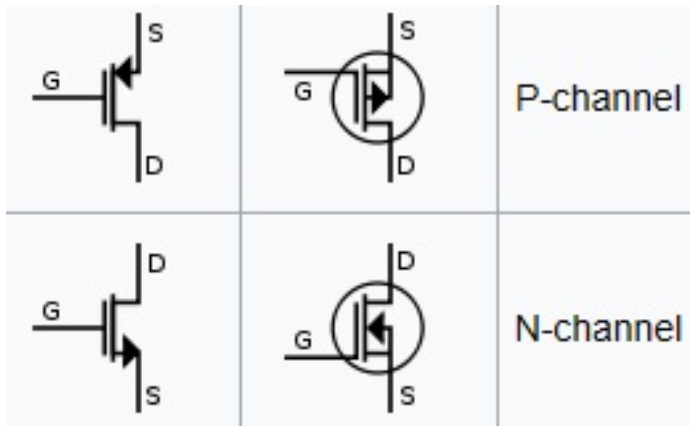

BJT(주로 증폭기능)는 Base, Collector, Emitter로 구성되며, MOSFET(주로 스위칭 작용)은 Gate, Drain, Source로 구성된다.

아래 그림은 반도체의 종류이다. 다이오드는 2개의 단자를 구성하고, 트랜지스터는 3개 이상의 단자를 구성한다.

트랜지스터는 접합형과 전계효과가 있다.

반도체 집적회로에는 주로 전계효과트랜지스터가 사용된다. 따라서 FET는 집적회로의 기본설계이기 때문에 플래쉬메모리(비휘발성), DRAM(휘발성)등은 기본 FET를 가지고 응용한 FET 반도체들이다.

전계효과트랜지스터(FET)는 게이트(G)에 전압을 걸어 발생하는 전기장에 의해 전자(-) 또는 양공(+)을 흐르게 하는 원리이다.

플로팅 게이트는 상부에 컨트롤 게이트가 존재하는 복층 구조가 특징이고, P채널과 N채널의 MOSFET 두개가 직렬로 구성되어 입력은 게이트에 출력은 드레인에 같이 연결된 CMOS(Complementary metal-oxide-semiconductor)가 있다.

CMOS는 상보적 MOS이다. MOS는 반도체 설계 기술이고, FET는 반도체 제품이다.

기술과 제품을 합쳐서 MOSFET이 된다.

CMOS는 두개의 PMOS와 NMOS가 상보적으로 합쳐진 트랜지스터이다.

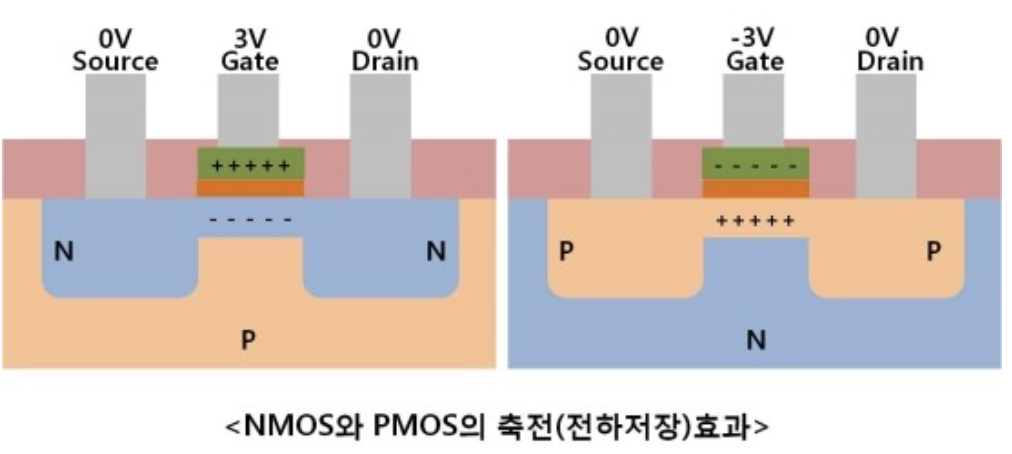

FET의 Gate와 금속 아래 유전체가 금속과 p형 반도체 사이에서 유전분극을 일으켜 금속과 반도체를 축전기처럼 이용해 전기장을 형성하게 만드는 역할을 한다.

소스(S)와 드레인(D)의 특별한 구분은 없고 상대적으로 전압이 더 낮은 곳이(S)이고, 전압이 더 높은 곳은 드레인(D)이 된다.

이것은 N형의 경우이고, P형은 그 반대가 된다.

기본적으로 N형과 P형의 차이는 소스와 드레인의 전류이동에 기여하는 캐리어가 전자(-)인지 양공(+)인지의 차이이다.

MOSFET도 다양한 종류가 있지만 가장 많이 사용되는 것은 MOS형으로, N형은 (자유)전자(-)가 이동하면 NMOS형, P형은 양공(+)이 이동하면 PMOS형으로 구분한다.

즉, MOSFET은 형성되는 채널의 종류에 따라 NMOS와 PMOS로 구성되며, 이 두가지가 직렬로 연결된 상보적인 CMOS가 있다.

2. 동작원리

NMOS의 원리로는

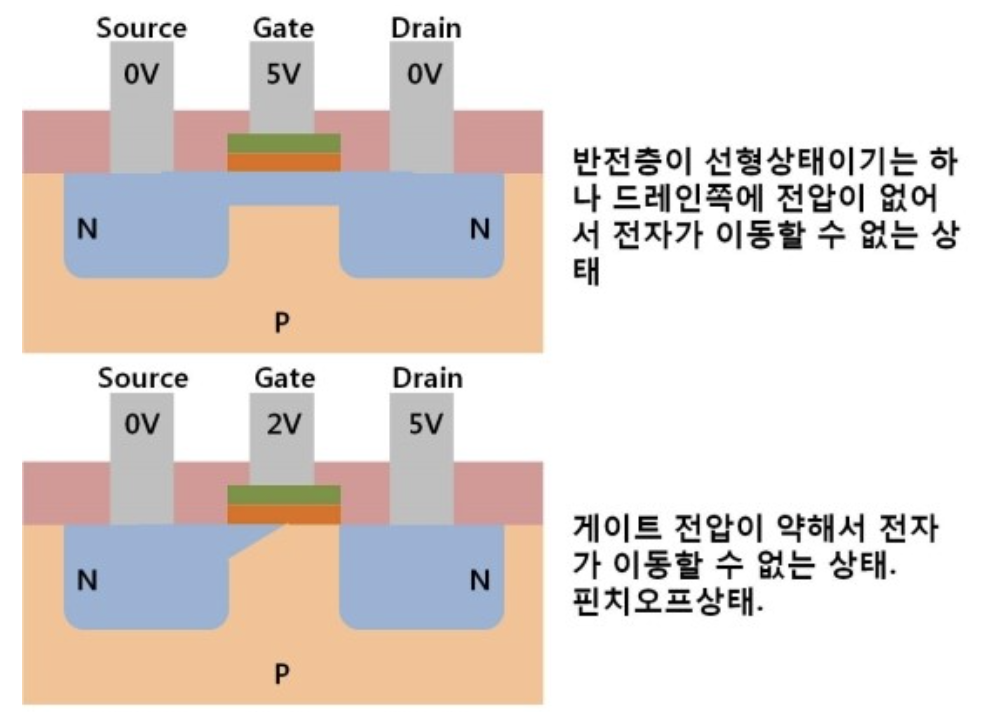

(1) 전류가 흐르지 않을 때

반도체 특성상 평상시에는 전류가 흐르지 않는다.

또한 게이트의 전압이 0V이거나 문턱전압(Threshold voltage)을 넘지 못할 정도로 낮을때도 전류가 흐르지 않는다.

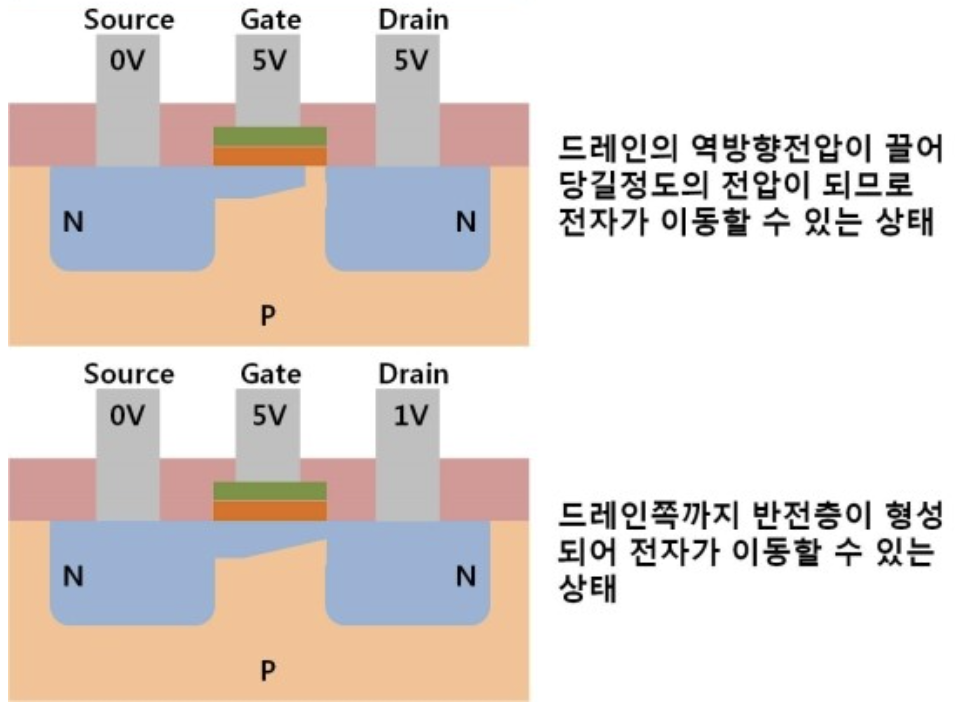

게이트의 순방향 전압은 드레인의 역방향 전압을 흐르게 하는데 도움을 준다.

(2) 전류가 흐를 때

전압이 소스와 게이트에 형성되는 문턱전압을 넘을 수 있는 전압이 게이트에서 걸리면 전자층이 형성된다.

이것이 이동 통로 역할을 한다.

게이트에 전압이 높아지면 축전기(유전체)가 p형 반도체와 축전기 사이에 전자를 끌어들여 N형 반도체처럼 되는 반전층을 형성시킴으로써, 전자가 p형 반도체를 통과해 드레인으로 이동할 수 있게 된다.

(전자가 이동하는 것이지만 전류의 이동이라고 생각해도 됌)

게이트의 전압을 높이면 반전층이 더욱 확대되면서 전자의 이동은 증가한다.

반전층이 넓어질수록 선형영역이 넓어지므로 컨덕턴스(conductance, 전류가 흐르기 쉬운 정도)가 증가한다.

게이트의 전압이 증가하면 전자의 이동이 많으나, 한계를 넘으면 포화되어 전류는 흐르지만 더이상 증가하지는 않는다.

드레인의 전압이 게이트 전압보다 커지면 공핍층이 형성되면서 반전층이 사라져 전류의 이동이 점차 차단된다.

이것을 핀치오프(pinch off)라고 한다.

(3) Gate의 전압에 따라 Drain의 전류량의 변화(전압제어로 전류조절)

전자를 이동시키며 또한 차단시킴으로 0 또는 1의 정보로 활용한다.

또한 게이트 쪽에 전하가 저장되어 있는지 아닌지의 여부로도 0 또는 1의 정보가 된다.

(게이트에 전하가 저장되어 있으면 소스에서 드레인 쪽으로 전류가 흐를 수 있게 된다. 또한 회로의 설계에 따라 축전기에 전하의 저장 유무로 구별하는 방법도 있다.)

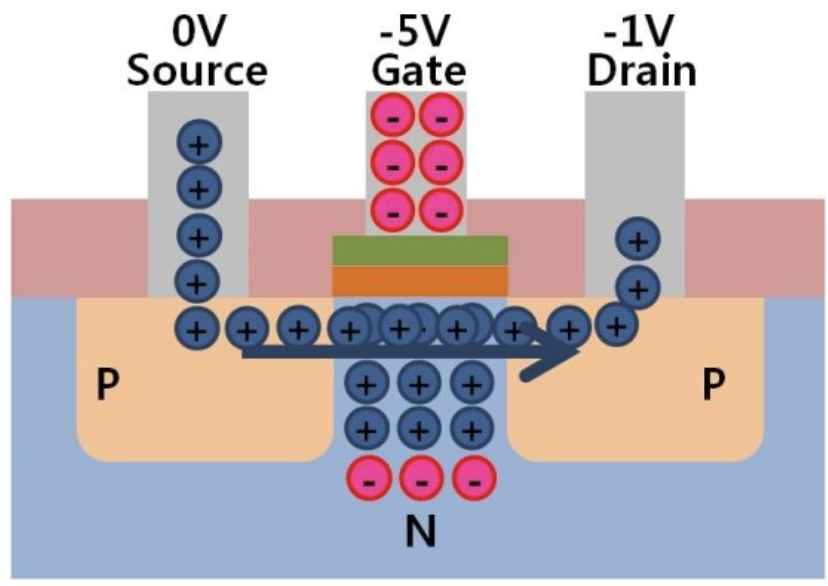

PMOS의 원리는

PMOS의 경우는 NMOS와 반대의 원리가 되며, 전압이 높은 소스(S)에서 전압이 낮은 드레인(D)로 양공(+)이 이동한다.

음(-)의 전압이 걸려 전류가 충분히 작아야 양공(+)이 이동한다.

즉, 전류가 흐르며, 양의 전압이 걸리면 채널은 사라지고 전류도 차단된다.

3. 기호

+참고

'Study > Power electronics' 카테고리의 다른 글

| Bootstrap(부트스트랩)회로 (0) | 2024.02.01 |

|---|---|

| Inverter Board analysis (0) | 2023.02.13 |

| Schmitt-Trigger 인코더 (0) | 2022.08.07 |

| PWM 제어 (회로적 접근) (0) | 2022.08.07 |

| 평활회로(AC->DC) (0) | 2022.08.02 |